Lab5manual

前言

上一次lab4中给我留下了阴影,我们看看中科大的ALU verilog内容。用这个题接口当框架。

正文

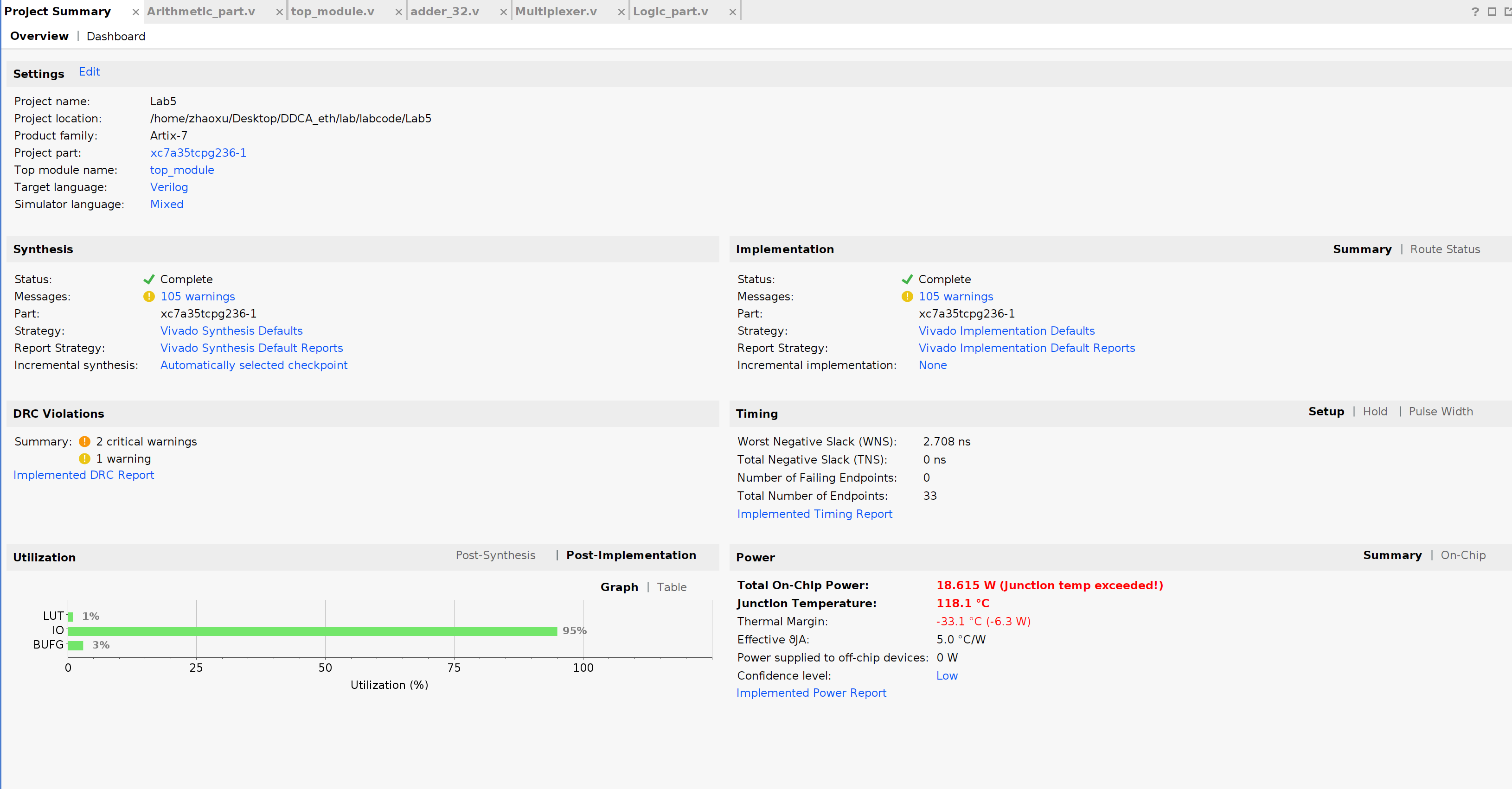

编写正确,但是在manual查看report的时候出现的问题,timing一直无法展现。我怀疑是语法正确但是整个ALU出现了问题,因此report和manual查看性能的部分都没完成,我打算先进行lab6,学习一下验证,回来再解决这个问题。

解决完了,我们回到实验五的工程里完成这个实验。

前面两个part是关于设计ALU和实现ALU的,我们直接参考manual的设计来,并且实现它,实现之后其实是有bug的,我们在lab6验证中先解决了bug反过来我们来看看part3

part3

我们按照manual要求,打开打开windows.

part3manual要求的填写部分写在下面。

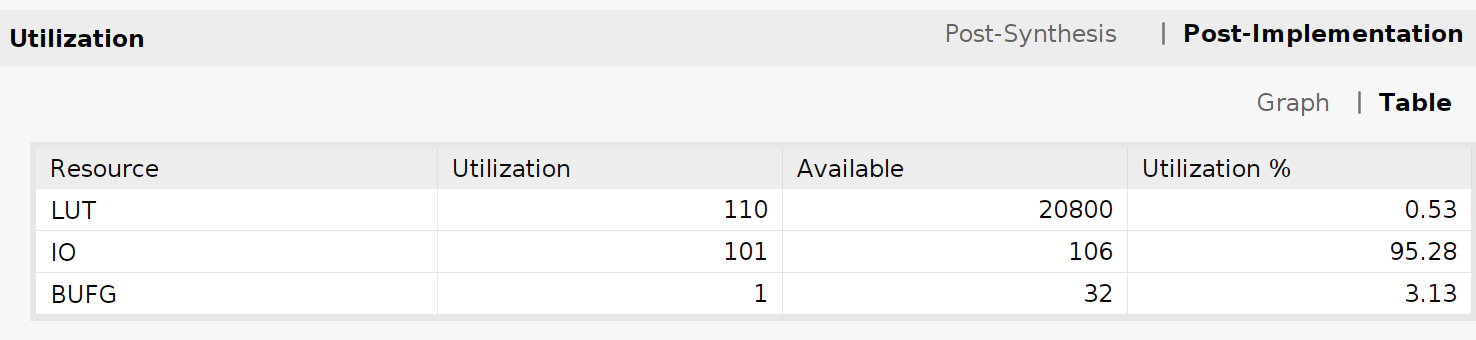

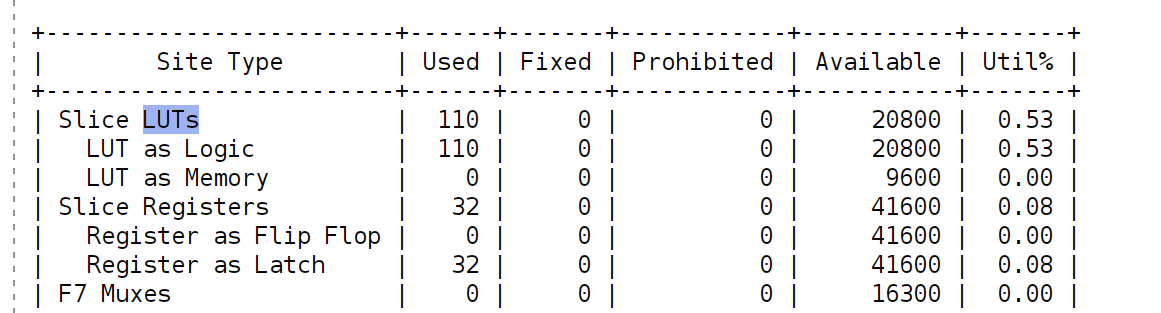

1. Number of LUTs

- 报告:Report Utilization

- 路径:

Reports > Report Utilization - 信息位置:在生成的资源使用报告中,可以看到 LUT 的数量,通常在 "Slice Logic" 部分,会列出

LUT的使用数量。

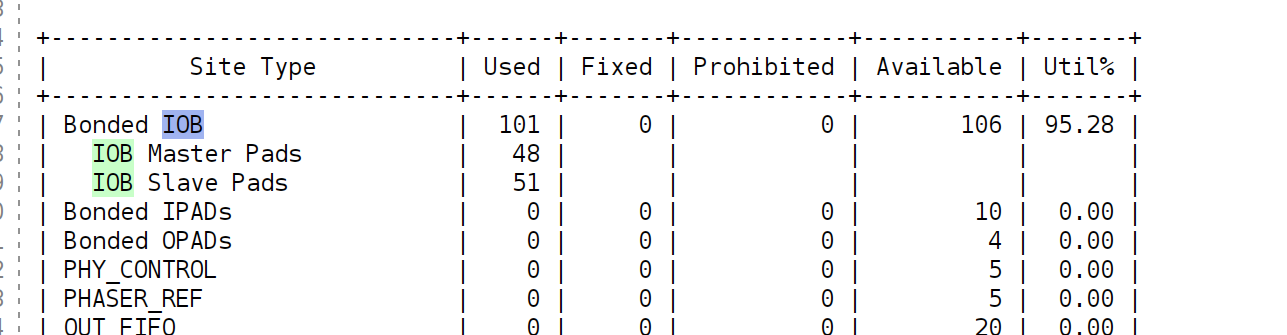

2. Number of bonded IOBs

- 报告:Report Utilization

- 路径:

Reports > Report Utilization - 信息位置:在 "I/O" 部分,可以找到

Bonded IOB的数量。

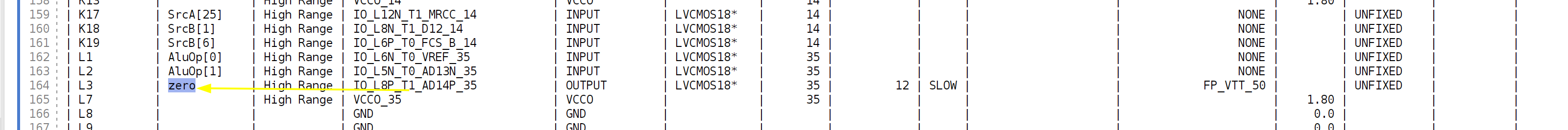

3. Which pin of the FPGA is the output 'zero' connected? (pin name)

- 报告:Report I/O Ports 或 Implemented Design

- 路径:

- 生成端口报告:

Reports > Report I/O Ports - 或者在Implemented Design中,查看Pinout报告。

- 生成端口报告:

- 信息位置:报告中会列出各个端口(例如 'zero')对应的 FPGA 引脚名称(pin name)。

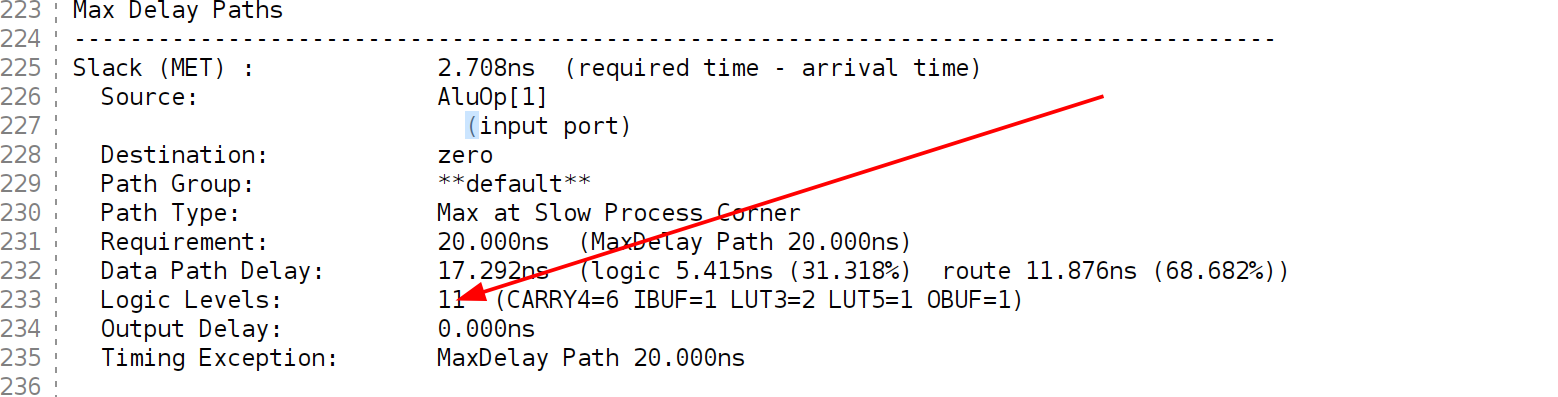

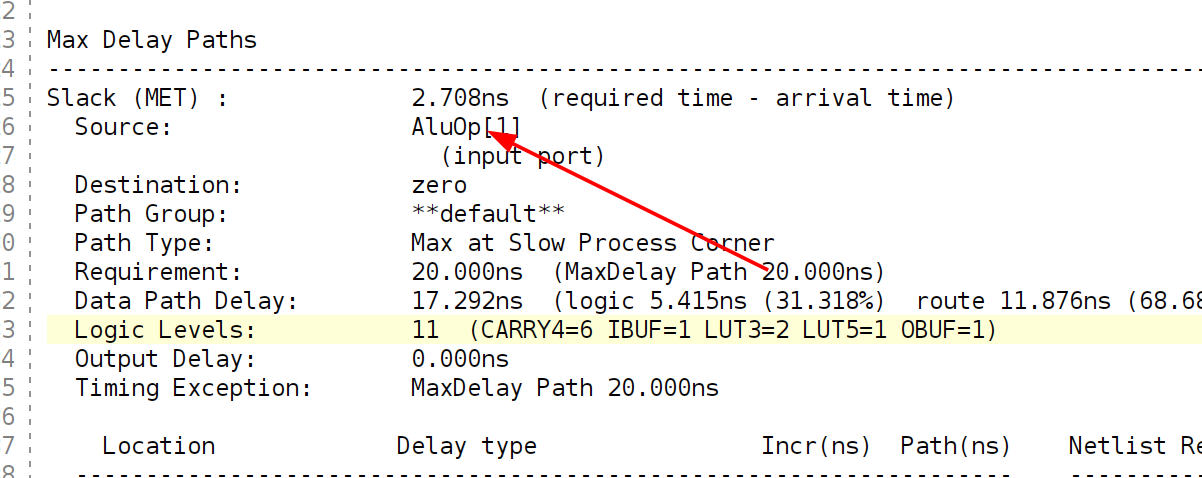

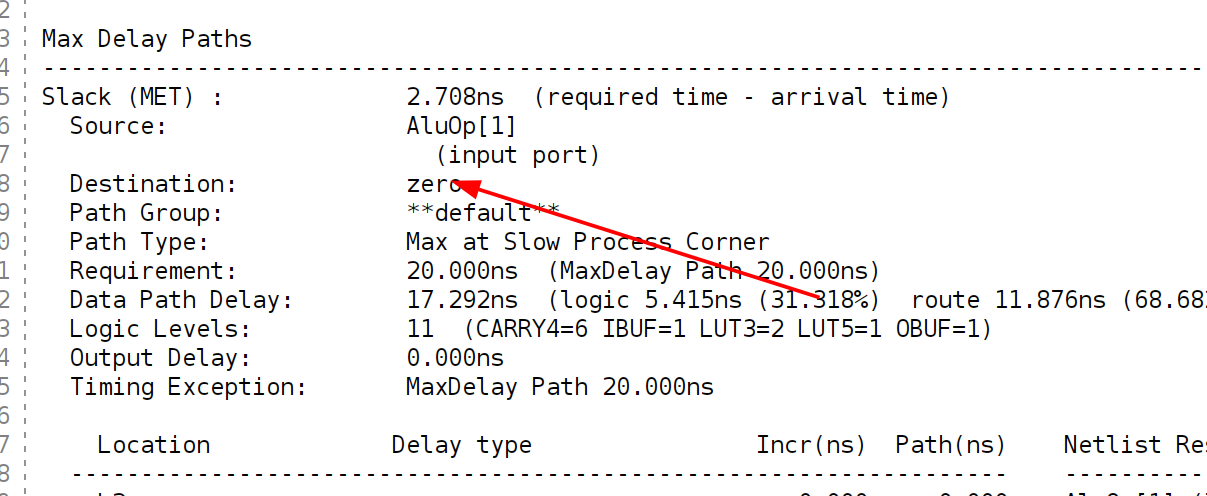

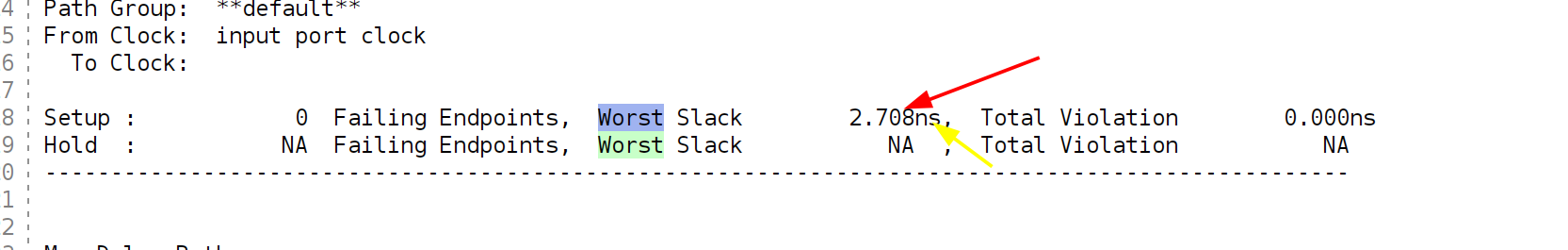

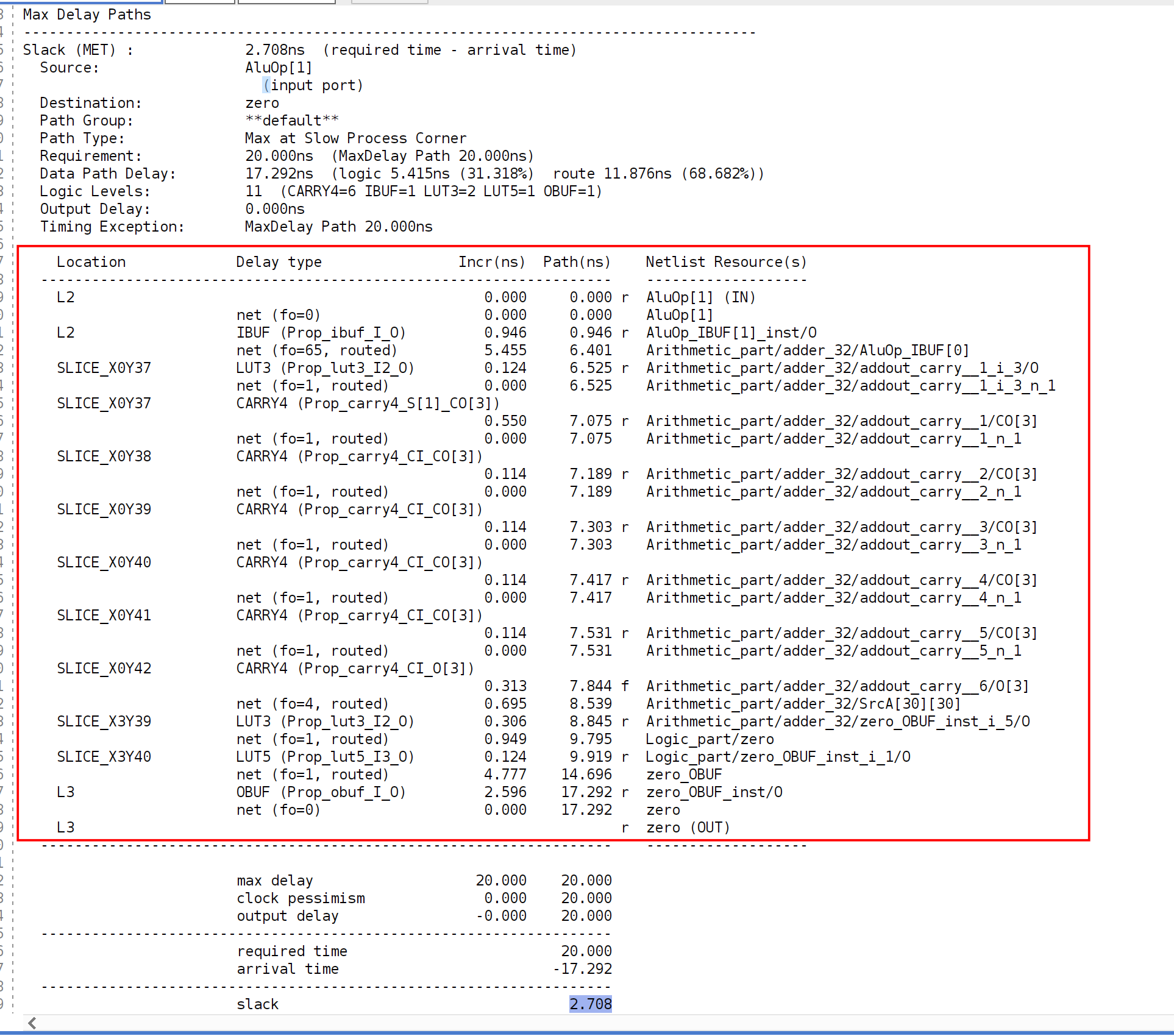

4. Where does the longest path start from

- 报告:Report Timing Summary

- 路径:

Reports > Report Timing Summary - 信息位置:查看时序路径中的起点,会有列出路径起始信号。

5. Where does the longest path end

- 报告:Report Timing Summary

- 路径:

Reports > Report Timing Summary - 信息位置:在同一个时序报告中,找到最长路径的终点信号。

6. How long is the longest path

- 报告:Report Timing Summary

- 路径:

Reports > Report Timing Summary - 信息位置:同样在时序报告中,可以看到每条路径的延迟时间,最长路径的延迟时间会被标记为“Worst Negative Slack”或类似字段。

7. How much of the longest path is routing

- 报告:Report Timing Summary

- 路径:

Reports > Report Timing Summary - 信息位置:在报告中查看各部分的时延贡献,通常可以看到逻辑和布线(routing)的时延分布。

8. How many levels of logic are in the longest path

- 报告:Report Timing Summary

- 路径:

Reports > Report Timing Summary - 信息位置:时序路径中会列出逻辑级数,可以找到最长路径涉及的逻辑级数。